Data Sheet September 9, 2005 FN2937.10

## 6-Bit, 30MSPS, Flash A/D Converter

The HI-5701 is a monolithic, 6-bit, CMOS flash Analog-to-Digital Converter. It is designed for high speed applications where wide bandwidth and low power consumption are essential. Its 30MSPS speed is made possible by a parallel architecture which also eliminates the need for an external sample and hold circuit. The HI-5701 delivers  $\pm 0.7$  LSB differential nonlinearity while consuming only 250mW (Typ) at 30MSPS. Microprocessor compatible data output latches are provided which present valid data to the output bus 1.5 clock cycles after the convert command is received. An overflow bit is provided to allow the series connection of two converters to achieve 7-bit resolution.

## **Ordering Information**

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG.<br>DWG.# |

|-------------|---------------------|------------|---------------|

| HI9P5701K-5 | 0 to 70             | 18 Ld SOIC | M18.3         |

### **Features**

- Overflow Bit

## **Applications**

- Video Digitizing

- Radar Systems

- · Communication Systems

• CMOS/TTL Compatible

· High Speed Data Acquisition Systems

### **Pinout**

(SOIC) TOP VIEW D5 (MSB) OVF 17 D3  $^{1}/_{2}R$ ٧ss NC 15 D2 CE2 D1 CE1 D0 (LSB) CLK 12  $V_{DD}$ PHASE 11 V<sub>REF</sub>+ 10 V<sub>REF</sub>

HI-5701

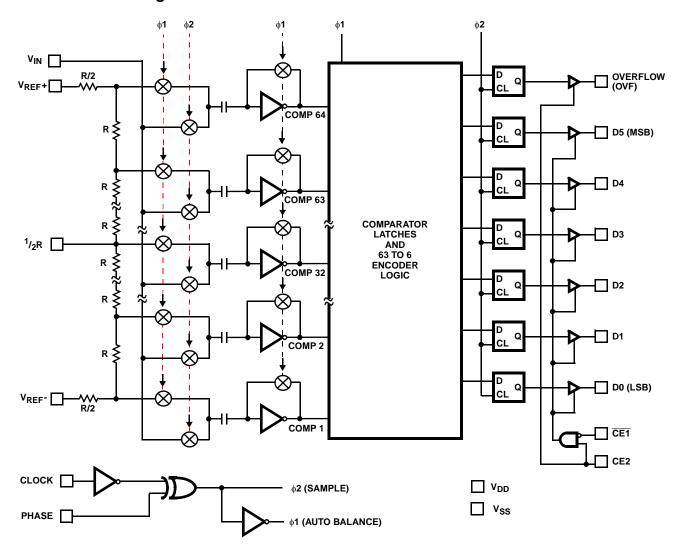

# Functional Block Diagram

## **Absolute Maximum Ratings**

Supply Voltage, V<sub>DD</sub> to V<sub>SS</sub> . . . . . . . . (V<sub>SS</sub> - 0.5) < V<sub>DD</sub> < +7V Analog and Reference Input Pins (V<sub>SS</sub> - 0.5) < V<sub>INA</sub> < (V<sub>DD</sub> +0.5V) Digital I/O Pins . . . . . . . . . . . (V<sub>SS</sub> - 0.5) < V<sub>I/O</sub> < (V<sub>DD</sub> +0.5V)

## **Operating Conditions**

| Temperature Range |        |      |

|-------------------|--------|------|

| HI9P5701-5        | 0°C to | 70°C |

### **Thermal Information**

| Thermal Resistance (Typical, Note 1)       | $\theta_{JA}$ (oc/w) |

|--------------------------------------------|----------------------|

| SOIC Package                               | . 80                 |

| Maximum Power Dissipation at 70°C (Note 2) | 635mW                |

| Maximum Junction Temperature               | 150 <sup>0</sup> C   |

| Maximum Storage Temperature Range          | 65°C to 150°C        |

| Maximum Lead Temperature (Soldering 10s)   | 300°C                |

| (SOIC - Lead Tips Only)                    |                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

- 2. Dissipation rating assumes device is mounted with all leads soldered to printed circuit board.

**Electrical Specifications**  $V_{DD} = +5.0V; V_{REF} = +4.0V; V_{REF} = V_{SS} = GND; f_S = Specified Clock Frequency at 50% Duty Cycle; <math>C_L = 30pF; Unless Otherwise Specified$

|                                                   |                                                      |     | 25°C  |       | (NO)<br>0°C T |       |        |

|---------------------------------------------------|------------------------------------------------------|-----|-------|-------|---------------|-------|--------|

| PARAMETER                                         | TEST CONDITIONS                                      | MIN | TYP   | MAX   | MIN           | MAX   | UNITS  |

| SYSTEM PERFORMANCE                                |                                                      | •   | •     |       | l             |       |        |

| Resolution                                        |                                                      | 6   | -     | -     | 6             | -     | Bits   |

| Integral Linearity Error, INL                     | $f_S = 20MHz$                                        | -   | ±0.5  | ±1.25 | -             | ±2.0  | LSB    |

| Best Fit Line)  Differential Linearity Error, DNL | $f_S = 30MHz$                                        | -   | ±1.5  | -     | -             | -     | LSB    |

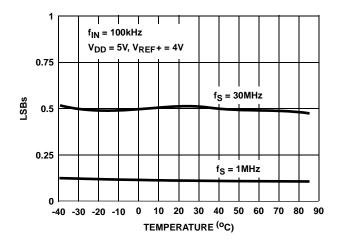

| Differential Linearity Error, DNL                 | $f_S = 20MHz$                                        | -   | ±0.3  | ±0.6  | -             | ±0.75 | LSB    |

| (Guaranteed No Missing Codes)                     | $f_S = 30MHz$                                        | -   | ±0.7  | -     | -             |       | LSB    |

| Offset Error, VOS                                 | f <sub>S</sub> = 20MHz (Note 3)                      | -   | ±0.5  | ±2.0  | -             | ±2.5  | LSB    |

| (Adjustable to Zero)                              | $f_S = 30MHz$                                        | -   | ±0.5  | -     | -             | -     | LSB    |

| Full Scale Error, FSE                             | f <sub>S</sub> = 20MHz (Note 3)                      | -   | ±0.25 | ±2.0  | -             | ±2.5  | LSB    |

| (Adjustable to Zero)                              | $f_S = 30MHz$                                        | -   | ±0.25 | -     | -             | -     | LSB    |

| DYNAMIC CHARACTERISTICS                           |                                                      |     |       |       |               |       |        |

| Maximum Conversion Rate                           | No Missing Codes                                     | 30  | 40    | -     | 30            | -     | MSPS   |

| Minimum Conversion Rate                           | No Missing Codes (Note 3)                            | -   | -     | 0.125 | -             | 0.125 | MSPS   |

| Full Power Input Bandwidth                        | $f_S = 30MHz$                                        | -   | 20    | -     | -             | -     | MHz    |

| Signal to Noise Ratio, SNR                        | $f_S = 1MHz$ , $f_{IN} = 100kHz$                     | -   | 36    | -     | -             | -     | dB     |

| = RMS Signal<br>RMS Noise                         | $f_S = 30MHz$ , $f_{IN} = 4MHz$                      | -   | 31    | -     | -             | -     | dB     |

| Signal to Noise Ratio, SINAD                      | $f_S = 1MHz$ , $f_{IN} = 100kHz$                     | -   | 35    | -     | -             | -     | dB     |

| = RMS Signal<br>RMS Noise + Distortion            | $f_S = 30MHz$ , $f_{IN} = 4MHz$                      | -   | 30    | -     | -             | -     | dB     |

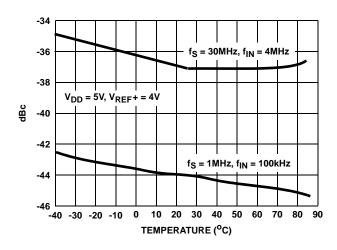

| Total Harmonic Distortion                         | $f_S = 1MHz$ , $f_{IN} = 100kHz$                     | -   | -44   | -     | -             | -     | dBc    |

|                                                   | $f_S = 30MHz$ , $f_{IN} = 4MHz$                      | -   | -38   | -     | -             | -     | dBc    |

| Differential Gain                                 | f <sub>S</sub> = 14.32MHz, f <sub>IN</sub> = 3.58MHz | -   | 2     | -     | -             | -     | %      |

| Differential Phase                                | f <sub>S</sub> = 14.32MHz, f <sub>IN</sub> = 3.58MHz | -   | 2     | -     | -             | -     | Degree |

| ANALOG INPUTS                                     | ·                                                    | •   | •     |       |               | •     |        |

| Analog Input Resistance, R <sub>IN</sub>          | V <sub>IN</sub> = 4V                                 | -   | 30    | -     | -             | -     | MΩ     |

| Analog Input Capacitance, C <sub>IN</sub>         | V <sub>IN</sub> = 0V                                 | -   | 20    | -     | -             | -     | pF     |

# **Electrical Specifications**

$V_{DD} = +5.0V; \ V_{REF} + = +4.0V; \ V_{REF} = V_{SS} = GND; \ f_S = Specified \ Clock \ Frequency \ at 50\% \ Duty \ Cycle; \ C_L = 30pF; \ Unless \ Otherwise \ Specified \ \textbf{(Continued)}$

|                                             |                                                |          | 25°C     |      | O°C T |      |       |

|---------------------------------------------|------------------------------------------------|----------|----------|------|-------|------|-------|

| PARAMETER                                   | TEST CONDITIONS                                | MIN      | TYP      | MAX  | MIN   | MAX  | UNITS |

| Analog Input Bias Current, IB               | V <sub>IN</sub> = 0V, 4V                       | -        | 0.01     | ±1.0 | -     | ±1.0 | μА    |

| REFERENCE INPUTS                            |                                                |          | +        | -    | +     | +    | !     |

| Total Reference Resistance, R <sub>L</sub>  |                                                | 250      | 370      | -    | 235   | -    | Ω     |

| Reference Resistance Tempco, T <sub>C</sub> |                                                | -        | +0.266   | -    | -     | -    | Ω/°C  |

| DIGITAL INPUTS                              |                                                | <u> </u> | *        |      |       |      |       |

| Input Logic High Voltage, VIH               |                                                | 2.0      | -        | -    | 2.0   | -    | V     |

| Input Logic Low Voltage, VIL                |                                                | -        | -        | 0.8  | -     | 0.8  | V     |

| Input Logic High Current, I <sub>IH</sub>   | V <sub>IN</sub> = 5V                           | -        | -        | 1.0  | -     | 1.0  | μА    |

| Input Logic Low Current, I <sub>IL</sub>    | V <sub>IN</sub> = 0V                           | -        | -        | 1.0  | -     | 1.0  | μА    |

| Input Capacitance, C <sub>IN</sub>          |                                                | -        | 7        | -    | -     | -    | pF    |

| DIGITAL OUTPUTS                             |                                                | <u> </u> | *        |      |       |      |       |

| Output Logic Sink Current, I <sub>OL</sub>  | V <sub>O</sub> = 0.4V                          | 3.2      | -        | -    | 3.2   | -    | mA    |

| Output Logic Source Current, IOH            | V <sub>O</sub> = 4.5V                          | -3.2     | -        | -    | -3.2  | -    | mA    |

| Output Leakage, I <sub>OFF</sub>            | CE2 = 0V                                       | -        | -        | ±1.0 | -     | ±1.0 | μА    |

| Output Capacitance, C <sub>OUT</sub>        | CE2 = 0V                                       | -        | 5.0      | -    | -     | -    | pF    |

| TIMING CHARACTERISTICS                      |                                                | <u> </u> | <u>'</u> | I    | l     | 1    | J.    |

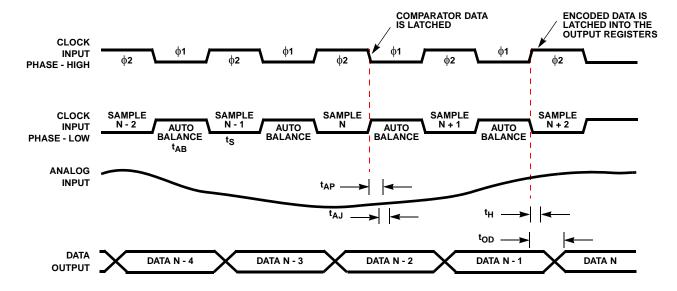

| Aperture Delay, t <sub>AP</sub>             |                                                | -        | 6        | -    | -     | -    | ns    |

| Aperture Jitter, t <sub>AJ</sub>            |                                                | -        | 30       | -    | -     | -    | ps    |

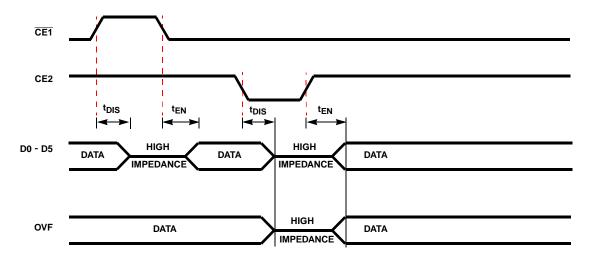

| Data Output Enable Time, t <sub>EN</sub>    | (Note 3)                                       | -        | 12       | 20   | -     | 20   | ns    |

| Data Output Disable Time, t <sub>DIS</sub>  | (Note 3)                                       | -        | 11       | 20   | -     | 20   | ns    |

| Data Output Delay, t <sub>OD</sub>          | (Note 3)                                       | -        | 14       | 20   | -     | 20   | ns    |

| Data Output Hold, t <sub>H</sub>            | (Note 3)                                       | 5        | 10       | -    | 5     | -    | ns    |

| POWER SUPPLY REJECTION                      |                                                |          |          |      |       |      |       |

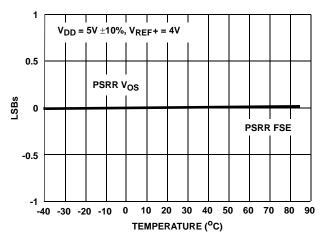

| Offset Error PSRR, ∆V <sub>OS</sub>         | V <sub>DD</sub> = 5V ±10%                      | -        | ±0.1     | ±1.0 | -     | ±1.5 | LSB   |

| Gain Error PSRR, ∆FSE                       | V <sub>DD</sub> = 5V ±10%                      | -        | ±0.1     | ±1.0 | -     | ±1.5 | LSB   |

| POWER SUPPLY CURRENT                        | <u>,                                      </u> |          |          |      |       |      |       |

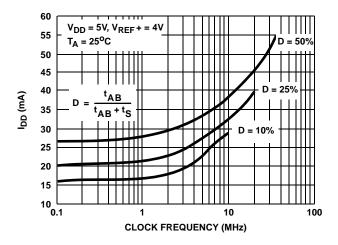

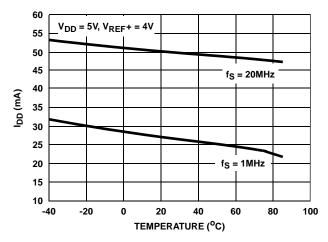

| Supply Current, I <sub>DD</sub>             | $f_S = 20MHz$                                  | -        | 50       | 60   | -     | 75   | mA    |

#### NOTE:

3. Parameter guaranteed by design or characterization and not production tested.

# **Timing Waveforms**

FIGURE 1. INPUT-TO-OUTPUT TIMING

FIGURE 2. OUTPUT ENABLE TIMING

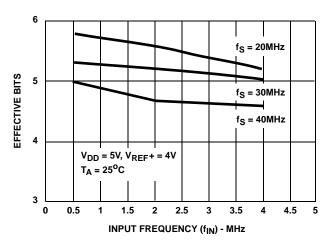

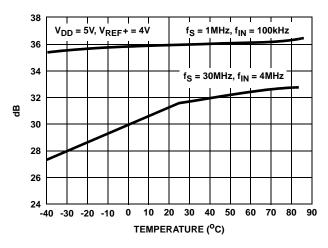

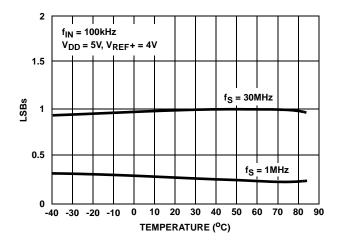

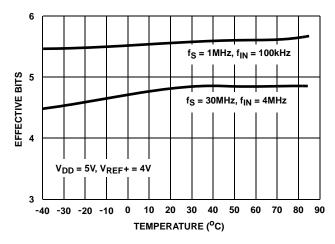

# **Typical Performance Curves**

FIGURE 3. EFFECTIVE NUMBER OF BITS vs fin

FIGURE 5. SNR vs TEMPERATURE

FIGURE 7. INL vs TEMPERATURE

FIGURE 4. ENOB vs TEMPERATURE

FIGURE 6. TOTAL HARMONIC DISTORTION vs TEMPERATURE

FIGURE 8. DNL vs TEMPERATURE

## Typical Performance Curves (Continued)

FIGURE 9. POWER SUPPLY REJECTION vs TEMPERATURE

FIGURE 11. SUPPLY CURRENT vs CLOCK AND DUTY CYCLE

FIGURE 10. SUPPLY CURRENT vs TEMPERATURE

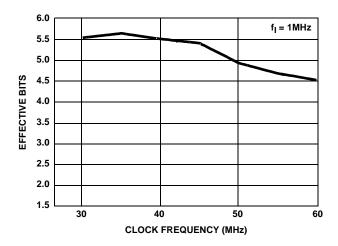

FIGURE 12. EFFECTIVE NUMBER OF BITS vs CLOCK FREQUENCY

**TABLE 1. PIN DESCRIPTIONS**

| PIN# | NAME                           | DESCRIPTION                                                                                                                                                           |

|------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | D5                             | Bit 6, Output (MSB).                                                                                                                                                  |

| 2    | OVF                            | Overflow, Output.                                                                                                                                                     |

| 3    | V <sub>SS</sub>                | Digital Ground.                                                                                                                                                       |

| 4    | NC                             | No Connection.                                                                                                                                                        |

| 5    | CE2                            | Three-State Output Enable Input, Active High (See Table 2).                                                                                                           |

| 6    | CE1                            | Three-State Output Enable Input, Active Low (See Table 2).                                                                                                            |

| 7    | CLK                            | Clock Input.                                                                                                                                                          |

| 8    | PHASE                          | Sample Clock Phase Control Input. When Phase is Low, Sample Unknown (φ1) Occurs When the Clock is Low and Auto Balance (φ2) Occurs When the Clock is High (See Text). |

| 9    | V <sub>REF</sub> +             | Reference Voltage Positive Input.                                                                                                                                     |

| 10   | V <sub>REF</sub> -             | Reference Voltage Negative Input.                                                                                                                                     |

| 11   | V <sub>IN</sub>                | Analog Signal Input.                                                                                                                                                  |

| 12   | $V_{DD}$                       | Power Supply, +5V.                                                                                                                                                    |

| 13   | D0                             | Bit 1, Output (LSB).                                                                                                                                                  |

| 14   | D1                             | Bit 2, Output.                                                                                                                                                        |

| 15   | D2                             | Bit 3, Output.                                                                                                                                                        |

| 16   | <sup>1</sup> / <sub>2</sub> R2 | Reference Ladder Midpoint.                                                                                                                                            |

| 17   | D3                             | Bit 4, Output.                                                                                                                                                        |

| 18   | D4                             | Bit 5, Output.                                                                                                                                                        |

TABLE 2. CHIP ENABLE TRUTH TABLE

| CE1 | CE2 | D0 - D5     | OVF         |

|-----|-----|-------------|-------------|

| 0   | 1   | Valid       | Valid       |

| 1   | 1   | Three-State | Valid       |

| Х   | 0   | Three-State | Three-State |

X = Don't Care

# Theory of Operation

The HI-5701 is a 6-bit analog-to-digital converter based on a parallel CMOS "flash" architecture. This flash technique is an extremely fast method of A/D conversion because all bit decisions are made simultaneously. In all, 64 comparators are used in the HI-5701; 63 comparators to encode the output word, plus an additional comparator to detect an overflow condition.

The CMOS HI-5701 works by alternately switching between a "Sample" mode and an "Auto Balance" mode. Splitting up the comparison process in this CMOS technique offers a number of significant advantages. The offset voltage of each CMOS comparator is dynamically canceled with each conversion cycle such that offset voltage drift is virtually

eliminated during operation. The block diagram and timing diagram illustrate how the HI-5701 CMOS flash converter operates.

The input clock which controls the operation of the HI-5701 is first split into a non-inverting  $\phi 1$  clock and an inverting  $\phi 2$  clock. These two clocks, in turn, synchronize all internal timing of analog switches and control logic within the converter.

In the "Auto Balance" mode ( $\phi$ 1), all  $\phi$ 1 switches close and  $\phi$ 2 switches open. The output of each comparator is momentarily tied to its own input, self-biasing the comparator midway between V<sub>SS</sub> and V<sub>DD</sub> and presenting a low impedance to a small input capacitor. Each capacitor, in turn, is connected to a reference voltage tap from the resistor ladder. The Auto Balance mode quickly precharges all 64 input capacitors between the self-bias voltage and each respective tap voltage.

In the "Sample" mode ( $\phi$ 2), all  $\phi$ 1 switches open and  $\phi$ 2 switches close. This places each comparator in a sensitive high gain amplifier configuration. In this open loop state, the input impedance is very high and any small voltage shift at the input will drive the output either high or low. The \$\psi 2\$ state also switches each input capacitor from its reference tap to the input signal. This instantly transfers any voltage difference between the reference tap and input voltage to the comparator input. All 64 comparators are thus driven simultaneously to a defined logic state. For example, if the input voltage is at mid-scale, capacitors precharged near zero during \$1 will push comparator inputs higher than the self bias voltage at \$\psi 2\$; capacitors precharged near the reference voltage push the respective comparator inputs lower than the bias point. In general, all capacitors precharged by taps above the input voltage force a "low" voltage at comparator inputs; those precharged below the input voltage force "high" inputs at the comparators.

During the next  $\phi 1$  state, comparator output data is latched into the encoder logic block and the first stage of encoding takes place. The following  $\phi 2$  state completes the encoding process. The 6 data bits (plus overflow bit) are latched into the output flip-flops at the next falling clock edge. The Overflow bit is set if the input voltage exceeds  $V_{REF} + - \frac{1}{2}$  LSB. The output bus may be either enabled or disabled according to the state of  $\overline{CE1}$  and CE2 (See Table 2). When disabled, output bits assume a high impedance state.

As shown in the timing diagram, the digital output word becomes valid after the second  $\phi 1$  state. There is thus a one and a half cycle pipeline delay between input sample and digital output. "Data Output Delay" time indicates the slight time delay for data to become valid at the end of the  $\phi 1$  state. Refer to the Glossary of Terms for other definitions.

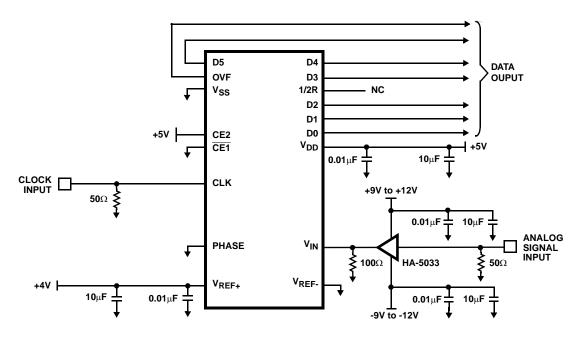

FIGURE 13. TEST CIRCUIT

# Application Information

### Voltage Reference

The reference voltage is applied across the resistor ladder at the input of the converter, between  $V_{REF}$ + and  $V_{REF}$ -. In most applications,  $V_{REF}$ - is simply tied to analog ground such that the reference source drives  $V_{REF}$ +. The reference must be capable of supplying enough current to drive the minimum ladder resistance of  $235\Omega$  over temperature.

The HI-5701 is specified for a reference voltage of 4.0V, but will operate with voltages as high as the  $V_{DD}$  supply. In the case of 4.0V reference operation, the converter encodes the analog input into a binary output in LSB increments of  $(V_{REF}+-V_{REF})/64$ , or 62.5mV. Reducing the reference voltage reduces the LSB size proportionately and thus increases linearity errors. The minimum practical reference voltage is about 2V. Because the reference voltage terminals are subjected to internal transient currents during conversion, it is important to drive the reference pins from a low impedance source and to decouple thoroughly. Again, ceramic and tantalum  $(0.01\mu F$  and  $10\mu F)$  capacitors near the package pin are recommended. It is not necessary to decouple the  $^{1}/_{2}R$  tap point pin for most applications.

It is possible to elevate  $V_{REF}$ - from ground if necessary. In this case, the  $V_{REF}$ - pin must be driven from a low impedance reference capable of sinking the current through the resistor ladder. Careful decoupling is again recommended.

## Digital Control and Interface

The HI-5701 provides a standard high speed interface to external CMOS and TTL logic families. Four digital inputs are provided to control the function of the converter. The clock

and phase inputs control the sample and auto balance modes. The digital outputs change state on the clock phase which begins the sample mode. Two chip enable inputs control the three-state outputs of output bits D0 through D5 and the Overflow OVF bit. As indicated in Table 2, all output bits are high impedance when CE2 is low, and output bits D0 through D5 are independently controlled by  $\overline{\text{CE1}}$ .

Although the Digital Outputs are capable of handling typical data bus loading, the bus capacitance charge/discharge currents will produce supply and local ground disturbances. Therefore, an external bus driver is recommended.

#### Clock

The clock should be properly terminated to digital ground near the clock input pin. Clock frequency defines the conversion frequency and controls the converter as described in the "Theory of Operation" section. The Auto Balance  $\phi 1$  half cycle of the clock may be reduced to 16ns; the Sample  $\phi 2$  half cycle may be varied from a minimum of 16ns to a maximum of  $8\mu s$ .

**TABLE 3. PHASE CONTROL**

| CLOCK | PHASE | INTERNAL GENERATION    |

|-------|-------|------------------------|

| 0     | 0     | Sample Unknown (\phi2) |

| 0     | 1     | Auto Balance (\phi1)   |

| 1     | 0     | Auto Balance (\phi1)   |

| 1     | 1     | Sample Unknown (\phi2) |

#### Gain and Offset Adjustment

In applications where accuracy is of utmost importance, three adjustments can be made; i.e., offset, gain, and

midpoint trim. In general, offset and gain correction can be done in the preamp circuitry.

### Offset Adjustment

The preferred offset correction method is to introduce a DC component to  $V_{IN}$  of the converter. An alternate method is to adjust the  $V_{REF}$ - input to produce the desired offset adjustment. The theoretical input voltage to produce the first transition is  $^{1}/_{2}$  LSB.

$V_{IN}$  (0 to 1 transition) =  $^{1}/_{2}$  LSB =  $^{1}/_{2}$ ( $V_{REF}/64$ ) =  $V_{REF}/128$ .

## Gain Adjustment

In general, full scale error correction can be done in the preamp circuitry by adjusting the gain of the op amp. An alternate method is to adjust the  $V_{REF}$ + input voltage. This adjustment is performed by setting  $V_{IN}$  to the 63 to overflow transition. The theoretical input voltage to produce the transition is  $^{1}/_{2}$  LSB less than  $V_{REF}$ + and is calculated as follows:

$V_{IN}$  (63 to 64 transition) =  $V_{REF}$  - ( $V_{REF}$ /128) =  $V_{REF}$ (127/128).

To perform the gain trim, first do the offset trim and then apply the required  $V_{\text{IN}}$  for the 63 to overflow transition. Now adjust  $V_{\text{RFF}}$ + until that transition occurs on the outputs.

## **Midpoint Trim**

The reference center ( $^{1}/_{2}$ R) is available to the user as the midpoint of the resistor ladder. The  $^{1}/_{2}$ R point can be used to improve linearity or create unique transfer functions. The offset and gain trims should be done prior to adjusting the midpoint. The theoretical transition from count 31 to 32 occurs at 31.5 LSBs. That voltage is calculated as follows:

$V_{IN}$  (31 to 32 transition) = 31.5( $V_{RFF}/64$ ) =  $V_{RFF}(63/128)$ .

An adjustable voltage follower can be used to drive the  $^{1}/_{2}R$  pin. Set  $V_{IN}$  to the 31 to 32 transition voltage, then adjust the voltage follower until the transition occurs on the output bits.

#### Signal Source

A current pulse is present at the analog input  $(V_{\mbox{\scriptsize IN}})$  at the beginning of every sample and auto balance period. The transient current is due to comparator charging and switch feed through in the capacitor array. It varies with the amplitude of the analog input and the sampling rate.

The signal source must be capable of recovering from the transient prior to the end of the sample period to ensure a valid signal for conversion. Suitable broad band amplifiers or buffers which exhibit low output impedance and high output drive include the HFA-0005, HA-5004, HA-5002, and HA-5033.

The signal source may drive above or below the power supply rails, but should not exceed 0.5V beyond the rails or damage may occur. Input voltages of -0.5V to  $+^{1}/_{2}$  LSB are converted to all zeros; input voltages of  $V_{REF}$ + -  $^{1}/_{2}$  LSB to  $V_{DD}$  + 0.5 are converted to all ones with the Overflow bit set.

### **Power Supply**

The HI-5701 operates nominally from a 5V supply, but will function from 3V to 6V. The supply should be well regulated and "clean" of significant noise, especially high frequency noise. It is recommended that power supply decoupling capacitors be placed as close to the supply pin as possible. A combination of  $0.01\mu F$  ceramic and  $10\mu F$  tantalum capacitors is recommended for this purpose as shown in the test circuit Figure 13.

#### **Reducing Power Consumption**

Power dissipation in the HI-5701 is related to clock frequency and clock duty cycle. For a fixed 50% clock duty cycle, power may be reduced by lowering the clock frequency. For a given conversion frequency, power may be reduced by shortening the Auto Balance  $\phi 1$  portion of the clock duty cycle.

| TARI | F 4 | OUT                  | PUT | CODE | <b>TABLE</b> |

|------|-----|----------------------|-----|------|--------------|

|      |     | $\sim$ $\sim$ $\sim$ |     |      |              |

|                                | INPUT VOLTAGE†                                     | E† BINARY OUTPUT CODE |     |     |    |    | T CODE |    |     |

|--------------------------------|----------------------------------------------------|-----------------------|-----|-----|----|----|--------|----|-----|

| CODE                           | V <sub>REF</sub> + = 4V<br>V <sub>REF</sub> - = 0V | DECIMAL               |     | MSB |    |    |        |    | LSB |

| DESCRIPTION                    | (V)                                                | COUNT                 | OVF | D5  | D4 | D3 | D2     | D1 | D0  |

| Overflow (OVF)                 | 4.000                                              | 127                   | 1   | 1   | 1  | 1  | 1      | 1  | 1   |

| Full Scale (FS)                | 3.9063                                             | 63                    | 0   | 1   | 1  | 1  | 1      | 1  | 1   |

| FS - 1 LSB                     | 3.8438                                             | 62                    | 0   | 1   | 1  | 1  | 1      | 1  | 0   |

|                                | •                                                  |                       |     |     |    | •  |        |    |     |

|                                |                                                    |                       |     |     |    | •  |        |    |     |

| <sup>3</sup> / <sub>4</sub> FS | 2.9688                                             | 48                    | 0   | 1   | 1  | 0  | 0      | 0  | 0   |

|                                | •                                                  |                       |     |     |    | •  |        |    |     |

|                                | •                                                  |                       |     |     |    | •  |        |    |     |

|                                | •                                                  |                       |     |     |    | •  |        |    |     |

TABLE 4. OUTPUT CODE TABLE (Continued)

|                                | INPUT VOLTAGE†                                     |         |     |     | BINAR | Y OUTPUT | CODE |    |     |

|--------------------------------|----------------------------------------------------|---------|-----|-----|-------|----------|------|----|-----|

| CODE<br>DESCRIPTION            | V <sub>REF</sub> + = 4V<br>V <sub>REF</sub> - = 0V | DECIMAL |     | MSB |       |          |      |    | LSB |

|                                | (V)                                                | COUNT   | OVF | D5  | D4    | D3       | D2   | D1 | D0  |

| <sup>1</sup> / <sub>2</sub> FS | 1.9688                                             | 32      | 0   | 1   | 0     | 0        | 0    | 0  | 0   |

| <sup>1</sup> / <sub>4</sub> FS | 0.9688                                             | 16      | 0   | 0   | 1     | 0        | 0    | 0  | 0   |

| 1 LSB                          | 0.0313                                             | 1       | 0   | 0   | 0     | 0        | 0    | 0  | 1   |

| Zero                           | 0                                                  | 0       | 0   | 0   | 0     | 0        | 0    | 0  | 0   |

<sup>†</sup> The voltages listed above represent the ideal transition of each output code shown as a function of the reference voltage.

## Glossary of Terms

**Aperture Delay -** is The time delay between the external sample command (the rising edge of the clock) and the time at which the signal is actually sampled. This delay is due to internal clock path propagation delays.

Aperture Jitter,  $t_{AJ}$  - This is the RMS variation in the aperture delay due to variation of internal  $\phi 1$  and  $\phi 2$  clock path delays and variation between the individual comparator switching times.

Differential Linearity Error, DNL - The differential linearity error is the difference in LSBs between the spacing of the measured midpoint of adjacent codes and the spacing of ideal midpoints of adjacent codes. The ideal spacing of each midpoint is 1 LSB. The range of values possible is from -1 LSB (which implies a missing code) to greater than +1 LSB.

**Full Power Input Bandwidth** - Full power bandwidth is the frequency at which the amplitude of the fundamental of the digital output word has decreased 3dB below the amplitude of an input sine wave. The input sine wave has a peak-to-peak amplitude equal to the reference voltage. The bandwidth given is measured at the specified sampling frequency.

**Full Scale Error, FSE -** is The difference between the actual input voltage of the 63 to 64 code transition and the ideal value of V<sub>REF</sub>+ - 1.5 LSB. This error is expressed in LSBs.

**Integral Linearity Error, INL** - The integral linearity error is the difference in LSBs between the measured code centers and the ideal code centers. The ideal code centers are calculated using a best fit line through the converter's transfer function.

**LSB -** Least Significant Bit =  $(V_{REF} + - V_{REF} -)/64$ . All HI-5701 specifications are given for a 62.5mV LSB size  $V_{REF} + = 4V$ ,  $V_{REF} - = 0V$ .

Offset Error,  $V_{OS}$  - Offset error is the difference between the actual input voltage of the 0 to 1 code transition and the ideal value of  $V_{REF}$ - + 0.5 LSB.  $V_{OS}$  error is expressed in

**Power Supply Rejection Ratio, PSRR -** Is expressed in LSBs and is the maximum shift in code transition points due to a power supply voltage shift. This is measured at the 0 to 1 code transition point and the 62 to 63 code transition point with a power supply voltage shift from the nominal value of 5.0V.

**Signal to Noise Ratio, SNR -** SNR is the ratio in dB of the RMS signal to RMS noise at specified input and sampling frequencies.

**Signal to Noise and Distortion Ratio, SINAD -** Is the ratio in dB of the RMS signal to the RMS sum of the noise and harmonic distortion at specified input and sampling frequencies.

**Total Harmonic Distortion, THD -** Is the ratio in dBc of the RMS sum of the first five harmonic components to the RMS signal for a specified input and sampling frequency

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

## Die Characteristics

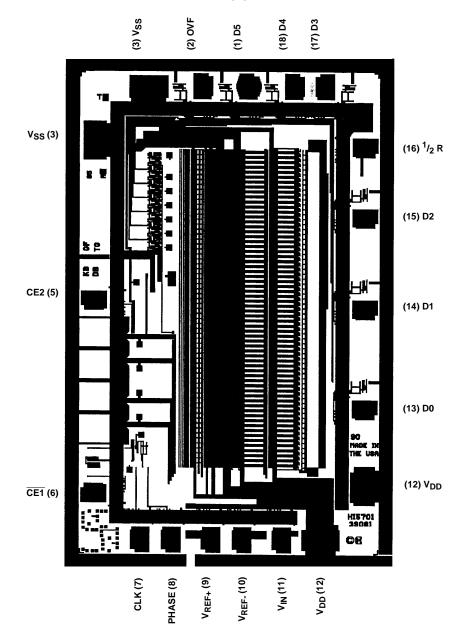

**DIE DIMENSIONS:**

86.6 mils x 130.7 mils x 19 mils  $\pm 1$  mil

METALLIZATION:

Type: SiAI

Thickness: 11kÅ ±1kÅ

PASSIVATION:

Type: SiO<sub>2</sub>

Thickness: 8kÅ ±1kÅ

**WORST CASE CURRENT DENSITY:**

<2.0 x 10<sup>5</sup> A/cm<sup>2</sup>

TRANSISTOR COUNT:

4000

SUBSTRATE POTENTIAL (POWERED UP):

V+

# Metallization Mask Layout

HI-5701